# A 5.99 GHZ INDUCTOR-LESS CURRENT CONTROLLED OSCILLATOR FOR HIGH SPEED COMMUNICATIONS

# Chakaravarty D Rajagopal<sup>1</sup>, Prof Dr.Othman Sidek<sup>2</sup>

<sup>1,2</sup>University Of Science Malaysia, 14300 NibongTebal, Penang. Malaysia <sup>1</sup>drchakra@pcocd2.intel.com <sup>2</sup>othman.cedec@usm.my

## ABSTRACT

This paper presents the design of five-stage current controlled inductor-less ring oscillator that were simulated in Silterra 0.18um CMOS Technology with oscillation frequencies up to 5.99 GHz. The design uses cross coupled MOS devices along with active inductor (thus inductor-less) and controlled by current source to aid in switching speed and to improve the noise parameters. The simulations show that the five-stage oscillator achieves frequency in the range of 3.78GHz to 5.99GHz. The simulated phase noise of the same design was -115.67 dBc/Hz at 1MHz offset with a center frequency of 5.99GHz.

#### **KEYWORDS**

VLSI &CMOS, LC Oscillators, Phase Noise, Current Source, Active Inductor

## **1. INTRODUCTION**

The Phase-locked Loop (PLL) is a critical component in many high-speed systems since it provides the timing basis for functions such as clock control, data recovery, and synchronization. The voltage/current controlled oscillators (VCO/CCO) is perhaps the most crucial element of the PLL because it directly provides output clock of the PLL.

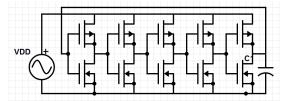

Any CMOS oscillators can be built using ring structures, relaxation circuits, or an LC resonant circuit. The LC design has the best noise and frequency performance due to the large Q factor of the resonant networks [1]. However, LC circuit in CMOS process increases the cost and the complexity of the chip and also often time creates problems in controlling the eddy current. On the other hand, oscillators with ring structure are easily built on any CMOS process and it is less complex and costly. The design is also very straight forward and it is also capable of providing multiphase outputs and a wide tuning range. Fig. 1 shows the conventional five-stage ring oscillator. The downside of this ring oscillator is compromised noise performance due to the

missing passive LC network. In this article, we present a design that improves the overall characteristics of CMOS ring oscillators to be comparable to those of LC designs by replacing the passive LC network with the active version. The design also adds a current source instead of voltage source to increase the switching speed.

Fig. 1Conventional Five-Stage Ring Oscillator

## 2. CROSS COUPLED DELAY CELL WITH ACTIVE INDUCTOR LOAD

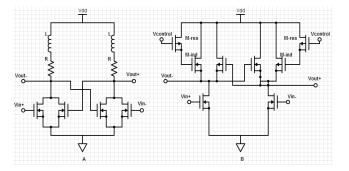

Fig.2(A) below shows the typical cross coupled delay cell with passive inductor load. These passive inductors in this circuit are realized using an on-chip spiral layout which suffers from huge area consumption, small inductance and strong interaction with the substrate. There are many ways to synthesize an inductor. Self-biased active inductors are one of them. There were some initial researches proposed for MESFET [2] and later re-developed for CMOS [3, 4]. Fig. 2(B) shows one such proposal.

Fig. 2 VCO delay cell. (A) delay cell with passive inductor. (B) delay cell with active inductor.

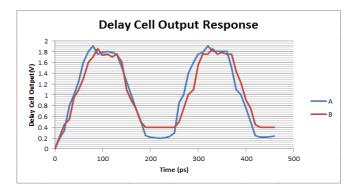

M-res and M-ind forms the active LRC network. The circuits in Fig. 2(A-B) are simulated with square wave input and the output response isshown in Fig. 3. Note that the output of the delay cell with active inductor (B) is very similar to the one with the passive inductor (A). This is a huge achievement in replacing the passive inductor with the active inductor.

Fig. 3 Output voltage of VCO delay cell.(A) Delaycell with passive inductor.(B) Delay cell with active inductor.

# **3. CURRENT MODE TECHNIQUE TO IMPROVE PHASE NOISE**

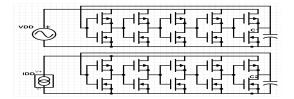

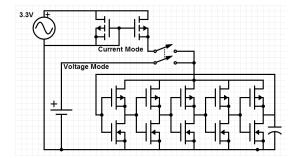

The oscillation frequency of a CMOS inverter ring oscillator can be tuned either by adjusting its core supply voltage  $V_{DD}$  or its core supply current  $I_{DD}$  as shown in Fig. 4 below.

Fig. 4. Conventional Ring Oscillator with voltage modesupply (top) and current mode supply (bottom).

Phase noise response for the five-stage conventional ring oscillator supplied with  $V_{DD}$  and  $I_{DD}$  are shown in the Table 1 below.

| Table 1. Simu | lation results of Phase Noise at 1MHz offset |

|---------------|----------------------------------------------|

| in V          | Voltage Mode and Current Mode.               |

| V <sub>DD</sub> (V)  | 2.3   | 1.8   | 1.3   |

|----------------------|-------|-------|-------|

| Phase Noise (dBc/Hz) | -88.7 | -81.8 | -79.1 |

| I <sub>DD</sub> (mA) | 5.4   | 3.5   | 1.6   |

| Phase Noise (dBc/Hz) | -92.3 | -85.4 | -82.7 |

It is clearly noted that the phase noise of the current controlled five-stage oscillator improves by about 4dBc/Hz as compared to voltage controlled. Silterra 0.18um CMOS technology was used in the design and simulation of the ring oscillator. To realize the current mode, PMOS current mirror technique implemented by using 3.3V I/O transistors. Fig. 5 depicts this.

Fig. 5 Conventional ring oscillator implementing PMOS current mirror and the connections for voltage mode and current mode supply.

## 4. PROPOSED INDUCTOR-LESS CURRENT CONTROLLED OSCILLATOR (ICCO)

Using the techniques described in Section 2 and Section 3 along with the negative delay skew techniques [5,6], a novel oscillator design has been proposed as shown in Fig. 6. Each stage of the

oscillator comprises of dual-delay cell with active inductor load scheme as depicted by Fig.2(B) and the PMOS current mirror for the current mode.

Fig. 6 Inductor-less Current Controlled Oscillator (ICCO)

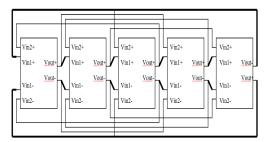

The oscillator is laid out in Silterra 0.18um CMOS technology and later the parameters were extracted for simulation purposes. Fig. 7 shows the layout of the oscillator.

| 2 |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

Fig. 7 Layout of Five-Stage ICCO.

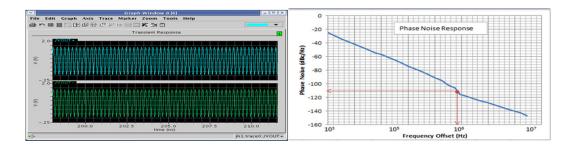

The extracted device parameters were simulated using the same 0.18um process. The simulation reveals a peak oscillation frequency 5.99GHz and simulated phase noise of -115.67dBc/Hz at the oscillation frequency of 5.99GHz at 1MHz offset as shown below in Fig. 8. The driving capacitance for this oscillator has been set to 0.5pF for each stage and the supply for the current mirror has been set to 3.3V.

Fig. 8Simulated ICCO Oscillation of 5.99GHz and phase noise of -115.67dBc/Hz at 1 MHz offset.

Numerous simulations were carried out with various  $I_{DD}$  settings. Table 2(A-B) below shows the simulation setup and the simulated output frequency and the phase noise of the ICCO for various setting of the  $I_{DD}$ . It is quite apparent that  $I_{DD}$  needs to be above 2mA for decent phase noise performance. Thus only a current mode circuit can provide such a large current for comparable voltage mode MOS device configurations.

170

|                               |                   | _                    |                      |         |         |        |         |        |

|-------------------------------|-------------------|----------------------|----------------------|---------|---------|--------|---------|--------|

| Simulation Setup              |                   | I <sub>DD</sub> (mA) |                      | 5.5     | 4.5     | 3.5    | 2.5     | 1.8    |

| Process                       | 0.18um CMOS       |                      | DD (IIIA)            | 2.0     | 4.5     | 2.0    | 2.5     | 1.0    |

| Voltage                       | 1.8v              | (                    | Osc Frequency (GHz)  | 5,99    | 5.45    | 5.16   | 4.97    | 3.7    |

| <b>Current Mirror Voltage</b> | 3.3v              | ·                    | Use Frequency (GH2)  | 3,33    | 5.45    | 5.10   | 4.37    | 5.70   |

| Driving Capacitance           | 5pF per stage     |                      | Phase Noise (dBc/Hz) | -115.67 | -113.45 | -111.2 | -107.89 | -87.25 |

| Simulation Tool               | Cadence's Spectre |                      | nuse noise (use/nz/  | 110.07  | 110,40  | 111.2  | 107.05  | 07120  |

(B)

Table 2. (A) Simulation Setup . (B) Simulated Oscillation Frequency and Phase Noise (at 1MHz offset) of the ICCO for various I<sub>DD</sub>

Table 3 below shows the comparison of this work against the other well-known works. It is clearly noted that this work excel in the oscillation frequency along with comparable phase noise. It is very interesting to note that the overall CMOS characteristics and process has improved dramatically when compared to the reported works especially [11] since it achieves almost same output frequency as this work. However, this work is much smaller in layout size (hence cheaper) since it is using active inductor as compared to passive inductor by [11] thus proving characteristics of CMOS has been improved through the replacement of passive inductor with active inductor.

Table 3. Comparison of this work against others

| Ref       | Technology (um) | Vdd (V) | Phase Noise (dBc/Hz) | Freq (GHz) |

|-----------|-----------------|---------|----------------------|------------|

| [7]       | 0.18 CMOS       | 1.8     | -118.00              | 3.0        |

| [8]       | 0.18 CMOS       | 1.8     | -110.00              | 1.6        |

| [9]       | 0.18 CMOS       | 1.8     | -122.90              | 1.6        |

| [10]      | 0.18 CMOS       | 1.8     | -109.40              | 1.5        |

| [11]      | 0.18 CMOS       | 1.8     | -101.67              | 6.01       |

| This Work | 0.18 CMOS       | 1.8     | -115.67              | 5.99       |

## **5.** CONCLUSIONS

(A)

This paper proposes a current controlled oscillator for an improved frequency oscillation and with active inductor load for an improved phase noise. Achieving a phase noise of -115.67 dBc/Hz at 1MHz frequency offset and a peak oscillation at 5.99GHz is quite obvious that this is capable of being used in high speed communications applications.

### REFERENCES

- B. Razavi, "A study of phase noise in CMOS oscillators", IEEE J. Solid-State Circuits, vol. 31, pp.331-343 1996

- [2] S. Hara, T. Tokumitsu, T. Tanaka and M. Aikawa, "Broadband monolithic microwave active inductor and its application to miniaturized wide-band amplifiers." IEEE Trans. Microwave Theory and Appl., vol. 36, no. 12, pp. 1920-1924, 1988.

- [3] E. Sackinger and W. Fischer, "A 3-GHz 32-dB CMOS limiting amplifier for SONET OC-48 receivers." IEEE J. Solid-State Circuits, vol. 35, no. 12, pp. 1884-1888, 2000.

- [4] S. Song, S.Park and H.Yoo, "A4-Gb/s CMOS clock and data recovery circuit using 1/8-rate clock technique." IEEE J. Solid-State Circuits, vol. 38, no. 7, pp. 1213-1219, 2003.

- [5] S.-J. Lee, B. Kim, and K. Lee, "A novel high-speed ring oscillator for multiphase clock generation using negative skewed-delay scheme", IEEE J. Solid-State Circuits, vol. 32, pp.289-291 1997

- [6] C. H. Park and B. Kim, "A low-noise, 900-MHz VCO in 0.6-µm CMOS", IEEE J. Solid-State Circuits, vol. 34, pp.586 -591 1999

- [7] L. Lu, H. Hsieh, Y. Liao, "A wide tuning-range CMOS VCO with a differential tunable active inductor", IEEE Transactions on Microwave Theory and Techniques, Vol. 54, No. 9, pp. 3462–3468, 2006

- [8] A. Tang, F. Yuan, E. Law, "A new CMOS active transformer QPSK modulator with optimal bandwidth control", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 55, No. 1, pp. 11–15, 2008

Computer Science & Information Technology (CS & IT)

- [9] A. Tang, F. Yuan, E. Law, "Class AB CMOS active transformers Voltage-Controlled Oscillators", ISSSE '07, International Symposium on Signals, Systems and Electronics, pp. 501–504, Montreal, 2007

- [10] A. Tang, F. Yuan, E. Law, "Low-noise CMOS active transformer voltage-controlled oscillators", MWSCAS 50th Midwest Symposium on Circuits and Systems, pp. 1441–1444, Montreal, 2007

- [11] N. Yangqing, C. Baoyong, W. Zhihua, "A CMOS LC VCO with 3.2-6.1GHz tuning range," Chinese Journal of Semiconductors, vol. 28, no. 4, pp. 526-529, 2007.

### **AUTHORS**

Chakaravarty D Rajagopalis currently a Member of Staff Engineer at Intel Corporation USA. He has been with Intel since 1995. He earned his Masters of Science in Microelectronics from University Science Malaysia in 2003 and currently working on his PhD. His current research interest includes VLSI, Microelectronics, CAD tools and various SoC verifications such as Gate level Simulations, Clock Domain Crossings, Synthesis, Formal Equivalence Verification and Static Timing Analysis.

Ó

Prof. Dr. Othman Sidek is currently a Prof at University Science Malaysia whose journey as an academian began 20+ years back. He is an esteemed Malaysian scientistand his charisma, talent and skills have enabled him to make meaningful contributions to Malaysia's nation building efforts. He earned his PhD in Information Systems Engineering from Bradford University, UK after completing Masters in Communication Engineering

from UMIST, UK. His current research areas mainly focus on Micro-Electro Mechanical Systems (MEMS), Wireless Sensor Network, Embedded System/SoC and VLSI/ASIC Designs.

172