# AN EFFICACIOUS RUNTIME ADAPTIVE HYBRID DRAM/PRAM MEMORY IN FPGA PLATFORM

M. Isaivani<sup>1</sup>, Dr. V. Malathi<sup>2</sup> and Dr.E.Sakthivel<sup>3</sup>

<sup>1</sup>Ph.D Scholar - Electrical Engineering, Anna University Regional Campus Madurai, Madurai, Tamil Nadu, India

<sup>2</sup>Professor, Department of Electrical and Electronics Engineering, Anna University Regional Campus Madurai, Madurai, Tamil Nadu, India

<sup>3</sup>Associate Professor, PSR Engineering College, Sivakasi, Tamil Nadu, India

## ABSTRACT

Hybrid main memory comprising of DRAM and PRAM becomes quite popular because of the less standby power benefit of PRAM and high performance of DRAM. In this work, the runtime-adaptive control and DRAM bypassing methods are introduced in order to minimize DRAM refresh energy that occupies a considerable portion of total system power. The work is carried out by using Xilinx 12.1 simulation tool and the experimental result proves that in the proposed work power consumption is greatly reduced i.e., only requires 3 %, with less area overhead while maintaining the speed parameter by comparing with the conventional method.

## **KEYWORDS**

Cache memory, Dynamic Random Access Memory, Phase-Change Random Access Memory, Write-back and Fill method

# **1. INTRODUCTION**

Currently, Very Large Scale Integration (VLSI) circuits are miniature in size to promote device functionalities and performance parameters. DRAM becomes a performance impediment in many systems due to the pin count, speed and pin bandwidth are risen extremely slowly. DRAM is one of the highest power consumers in modern computing systems. So that, power budget of DRAM is quite similar to or sometimes, even surpasses the power budget of CPU. It is proven that DRAM in a commercial system uses 25–45% of total system power. With this scenario, energy efficient DRAM has become a crucial design constraint for the system design.

Even DRAM performance emerges as a critical issue in the modern server systems because of the universal utilization of data-centric applications. Since DRAM bandwidth is not scalable and considered as a limited resource, huge contention exists in DRAM that debases total system performance significantly. To enhance DRAM performance and to lower dynamic-energy consumption, the row-level access locality should be enhanced and the count of row activations should be decreased. The row activations are considerably reduced by performing more read and write operations for each activated row. More row activations result in higher wastage of energy.

N. Ramasubramanian et al.(Eds) : SRAIC-2019 pp. 47-57, 2019. © CS & IT-CSCP 2019

DOI: 10.5121/csit.2019.91504

This paper analyzes DRAM activities and implements cache line write-backs and fill methods together with the hybrid DRAM/PRAM memory .In the proposed hybrid main memory, PRAM operates as a background main memory due to its low stand-by power benefit and DRAM serves as a cache owing to its low latency and lower power consumption during read and write operations. This hybrid main memory system takes advantage of both memories while reducing the negative aspect of limitations in both of them.

# 2. LITERATURE SURVEY

A brief survey of various techniques involved in data compression is presented for main memory and cache memory [1]. A set- and-way management approach is proposed in [2] for a runtime-reconfiguration of a cache's size and associativety. Deterministic nap technique and early miss detection approach are proposed in [3] in order to diminish static as well as dynamic power. "Latency-Programmable System Emulation Memory" is implemented in [4] that permits read-and/or-write latency scale-up capability. Direct data access can be achieved in eDRAM cache by proposing tag-comparison in memory that enhanced energy efficiency [5]. The "eXplicitMulti-Threading (XMT)" paradigm is designed for a Parallel Random Access Model on-chip processor [6].PRAM-On-Chip Phase Change Memory (PCM) provides higher capacity than DRAM and evolves for a greater capacity memory [7,8, 9, 10]. Gen2 Hybrid Memory Cube is characterized from data-centric demands. HMC offers considerable accessing bandwidth while requiring less power [11, 12]. Novel write algorithms for PCM are discussed detail in [13]. Retention-aware placement method is employed in DRAM to lessen refresh power [14]. In [15], statistical populations' method is proposed for DRAM cache and also inherent error-control technique is utilized to minimize refresh rate. Different techniques are discussed for utilizing memory controller in order to enhance energy efficiency of DRAM and also to manage power in DRAM [16]. Another multi-partition based memory controller BIBIM is designed that combines DRAM and PRAM [17]. Memory access scheduling technique is introduced in [18] that reorder memory references to improve the energy efficiency. An effective Collective write-back and fill method is employed for DRAM cache in order to enhance the data throughput [19].

# **3.** EXISTING SYSTEM

Collective Write-back-cum-Fill method [19] consists of the following two approaches: writeback strategy and fill strategy. It is executed by the feedback exists between Dynamic-Writeback-Unit (DWU) and Adaptive DRAM Placement (ADP) entities. The write-back strategy is carried out by DWU. When L3cache replacement occurs, checking is done on the victim line to find if it is dirty. If there is no any modified bit, the victim line is evacuated from L3cache without writing back to the DRAM cache. If the victim line is dirty, DWU will decide if writeback is to be done on DRAM cache. The line is added to the DRAM cache if affirmative decision is taken. Or else, DRAM cache hit/miss will be verified. The line should be introduced into DRAM cache with the condition that is a hit in order to maintain regularity. If not, the line is infused into main memory. Fill strategy is carried out by ADP entity which decides whether to add fill requests to DRAM cache.

The CWFP method requires two vital units: Integrated Set Monitors (ISM) and Lose-to-Gain Dispatcher (LGD). Based on the investigation of DRAM cache accessing management, the module ISM determines which activity to be performed on DRAM cache i.e., write-back or fill operation .An another appropriate entity called, Miss-Status Handling Register (MSHR) includes W and F bits to decide for write-back and fill cache operations respectively. This system offers LGD over ISM in the aim to avert needless write-back access to DRAM cache and it also aids to rectify the feasible wrong perception of ISM. Remarkably, LGD supports the

ISM's decision making capability and in the way DRAM interference got reduced. Moreover it evaluates the accuracy of write-back access based on per-core criteria and it curtails the cache resources allotment to useless write-backs.

- Though existing CWFP scheme reduced DRAM interference, inter-core contention and achieved greater speedup, it still suffered with higher power consumption of DRAM. The major amount of total power available in the system is consumed by this unit.

- The following section describes the proposed hybrid DRAM/PRAM scheme to address the above challenge.

# 4. PROPSED SYSTEM

#### 4.1. PRAM Overview

DRAM has been adopted for the main memory in computer systems for several years. Many non-volatile memories like Phase change RAM (PRAM), Magnetic RAM (MRAM) and Ferroelectric RAM (FRAM) are developed for future generation technologies. In these non-volatile memories (NVM), PRAM becomes popular entity for main memory due to its advantageous properties of low power requirement and high density. A PRAM cell is made up of phase change material for bit representation. PRAM density is very much larger than DRAM (expected to be about four times). Moreover, unvarying property of phase material after power-off, it exhibits petty leakage energy irrespective of memory size.

#### 4.2. Implementation

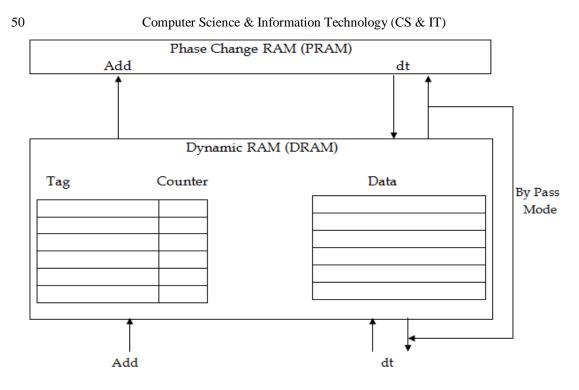

In this effective hybrid DRAM/PRAM method, DRAM plays as a last-level cache and operates as the working memory while PRAM performs as a massive background main memory. Figure 1 shows the architecture of this hybrid memory, where the memory controller manages the tag structure in DRAM and the counter governs each row in DRAM. By decaying the DRAM contents, power management can be achieved. If the data are clean, they are expelled from DRAM. For the modified data, they should be written back to PRAM before eviction. When the new data are written to DRAM which has been read from PRAM, global time-out value is set to the counter. The counter value is decreased by one periodically. It is again set to the time-out value after row access takes place. When the counter reaches zero, the row will be expelled. That removed row does not need refresh which leads to attain considerable energy saving. The following two methods are utilized to manage the power in the proposed scheme.

Add: Address; dt : Data

Figure 1. Hybrid DRAM/PRAM Memory Scheme

## 4.2.1. Runtime-Adaptive Control of Time-Out Value

This method is performed that reduces the total energy while satisfying system performance constraints. When time-out value increases, many rows in DRAM would be live and needs refreshes and so DRAM energy rises. But PRAM energy decreases and PRAM accesses are less because much data are accessed by DRAM with a huge hit rate. There is a best time-out value (BTO) that provides less total energy of the hybrid scheme by averting DRAM refreshes. The BTO value changes because of the dynamically varying manner in memory access.

## 4.2.2. Bypassing DRAM

DRAM bypassing is performed to the first read operation that fetches a miss in DRAM cache. When in the second access to the corresponding row in DRAM within the time-out value, the data in row are replicated to DRAM from PRAM and that row begins to be refreshed to perform further accesses. This method screens out memory accesses that have poor spatial locality and to enhance the DRAM refresh energy efficiency.

## 5. RESULTS AND DISCUSSION

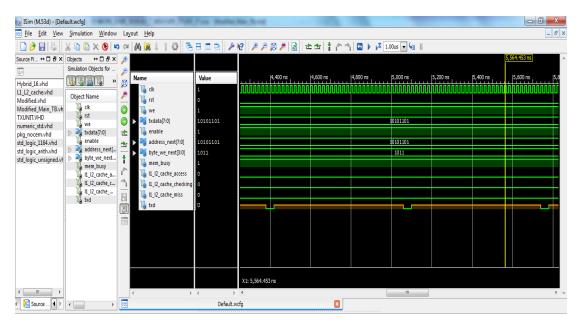

The proposed system is implemented in Xilinx 12.1 tool and written in VHDL (Very large scale integration Hardware Description Language) coding to perform evaluation for both existing cache write-back and fill method with proposed runtime-adaptive hybrid DRAM/PRAM schemes.

## 5.1. Performance Parameters of Existing System

#### 5.1.1. Area Consumption

The area requirements of slice registers, LUT, LUT –flip-flop pairs, bonded IOB buffers are 41, 44, 40, 18,1 respectively as shown in figure 2.

| Eile Edit View Project Source Process Tools Window       | Layout <u>H</u> elp                                            |                                   |                            |                                    |                     |           | -                    |

|----------------------------------------------------------|----------------------------------------------------------------|-----------------------------------|----------------------------|------------------------------------|---------------------|-----------|----------------------|

| ଅଟ୍ୟ 🤘 🖉 🖉 🖉 🖉 🖉 🗧                                       |                                                                | 🕨 🗴 🛠                             |                            |                                    |                     |           |                      |

| esign + C & X                                            | Design Overview                                                |                                   | Proposed                   | Main Project Status                | (04/11/2017 -       | 13:11:12) |                      |

| Yiew:                                                    | IOB Properties                                                 | Project File:                     | VER_27.xise                | Parser                             | Errors:             |           | No Errors            |

| Hierarchy                                                | Module Level Utilization                                       | Module Name:                      | Proposed_Main              | Imple                              | mentation Stat      | e:        | Synthesized          |

| □                                                        | Pinout Report                                                  | Target Device:                    | xc6vlx75t-3ff484           |                                    | Errors:             |           | No Errors            |

| 📄 🚡 🛐 Modified_tb - TB_ARCHITECTURE (Modified_Main_TE    | Clock Report                                                   | Product Version:                  | ISE 12.1                   |                                    | Warnings:           |           | 15 Warnings (13 new) |

| WUT - Modified - Modified (Modified.vhd)                 | Static Timing                                                  | Design Goal:                      | Balanced                   |                                    | Routing Result      | ts:       |                      |

| proposed_main_tb - TB_ARCHITECTURE (Proposed_N           | 🖥 🚽 📄 Parser Messages                                          | Design Strategy:                  | <u>Xilinx Default (unl</u> | ocked)                             | Timing Constraints: |           |                      |

| EF IN THE UUT - Proposed Iviain - Proposed Iviain (LP_AC | Synthesis Messages                                             | Environment:                      | System Settings            |                                    | Final Timing Se     | ore:      |                      |

| PR1 - L1_L2_cache - logic (L1_L2_cache.vhd)              | Map Messages                                                   |                                   |                            |                                    |                     |           |                      |

| PR3 - Processng_Element - Behaviour (TXUNI               | Place and Route Messages                                       |                                   | Device Utiliz              | ation Summary (esti                | imated values)      |           | Ŀ                    |

|                                                          | 👔 Timing Messages<br>🗋 Bitgen Messages                         | Logic Utilization                 |                            | Used                               | Available           |           | Utilization          |

|                                                          | - 📓 All Implementation Messages                                | Number of Slice Registers         |                            |                                    | 41                  | 93120     | 09                   |

| No Processes Running                                     | <ul> <li>Detailed Reports</li> <li>Synthesis Report</li> </ul> | Number of Slice LUTs              |                            |                                    | 44                  | 46560     | 09                   |

| Processes: UUT - Proposed_Main - Proposed_Main           |                                                                | Number of fully used LUT-FF pairs |                            |                                    | 40                  |           | 889                  |

| Design Summary/Reports                                   | Design Properties                                              | Number of bonded IOBs             |                            |                                    | 18                  | 240       | 79                   |

|                                                          | Optional Design Summary Contents                               | Number of BUFG/BUFGCTRLs          |                            |                                    | 1                   | 32        | 39                   |

| 👔 🐮 👹 User Constraints                                   | Show Clock Report                                              |                                   |                            |                                    |                     |           |                      |

| 🔋 🕀 🚺 Synthesize - XST                                   |                                                                |                                   |                            |                                    |                     |           |                      |

| ⊕ ₹11 Synthesize - XST<br>⊕ ₹110 Implement Design        | - Show Warnings                                                |                                   |                            |                                    |                     |           | E                    |

| Configure Target Device                                  | Show Warnings                                                  | Report Name                       | Status                     | Generated                          | Errors              | Warnings  | Infos                |

|                                                          |                                                                | Report Name Synthesis Report      | Status<br>Current          | Generated<br>Tue Apr 11 13:11:10 2 |                     | Warnings  |                      |

Figure 2. Area consumption of Existing System

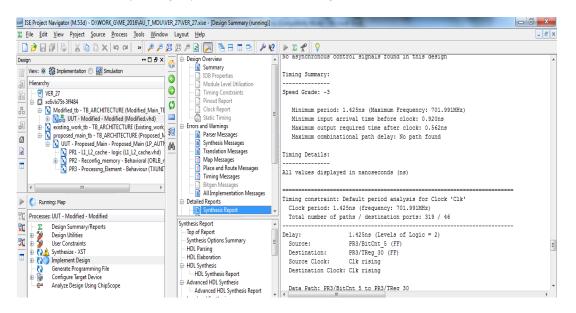

#### **5.1.2. Speed Evaluation**

The output shows the minimum required time and maximum frequency are 1.425ns and 701.991MHz respectively. The minimum input arrival time before clock, maximum output required time after clock, maximum combinational path delay are 0.929ns, 0.567ns, 0.289ns respectively. It is shown in figure 3.

| ISE Project Navigator (M.53d) - D:\WORK_G\ME_2016\AU_T_MDU\VER_2                                                       | 27\VER_27.xise - [Design Summary (Synthesized)]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                            |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 🔀 Eile Edit View Project Source Process Jools Window L                                                                 | .ayout <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ 6 :                                                      |

| 🗋 🏓 🗐 🖉 🐰 🛍 🗋 🗙 🕪 여 🕷 🎜 👰 🕻                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ▶ ∑ <b>𝕐</b> 💡                                             |

| Design       +• □ ∅ ×                                                                                                  | Design Overview     Sommary     Top Properties     Module Level Ublization     Timing Constants     Priout Report     Cock Report     Coc | Asynchronous Control Signals Information:<br>              |

| Generate Programming File     Generate Programming File     Configure Target Device     Analyze Design Using ChipScope | HDL Synthesis Report     Advanced HDL Synthesis     Advanced HDL Synthesis Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Source: PR3/BitCnt_5 (FF)<br>Destination: PR3/TReg_30 (FF) |

| Start Cesign C Files C Ubraries                                                                                        | I ow Lowel Supplication The InfoCenter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C Design Summary (Synthesized)                             |

Figure 3. Speed Evaluation of Existing System

## **5.1.3.** Power Consumption

52

The existing system which involves the collective write-back and fill method, requires 7.6% of total power available. It is computed from figure 4.

| 🖁 Xilinx XPower Analyzer - Existing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _work.ncd - [Table View]                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 骑 File Edit View Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| 1) 🗗 🖉 🗎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| Report Navigator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | × A B                                                                                                                                                                                                                                                                                                   | CDEFGHIJKLMN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ^ |

| Default Activity Rates     Summay     Confidence Level     Details     Details     Details     Details     Details     Default     De | Device     Family Vites6     Family Vites6     Part sc6vk75t     Package IN464     Grade Commercial      Process Typical     Speed Grade 3                                                                                                                                                              | On-Chip         Power (W)         Used         Available         Utilization (%)         Supply         Total         Dynamic         Duescent           Clocks         0.000         1         -         -         -         Source         Voltage         Current (A)         Current (A)         Current (A)           Logic         0.000         50         445560         0.1         Vocint         1.000         0.605         0.000         0.605           Signals         0.000         70         -         -         Vocint         2.500         0.044         0.000         0.040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| Color Source Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Environment Environment Environment Use curtom TiA(2) Head Sink Medium Profile  Lotom TSA(2) Head Sink Head Sink Head Layers B to 11  Lotom TiB(2) NA Board Layers B to 11  Lotom TiB(2) NA | Effective TJ& Max Ambient Junction Temp         Total         Dynamic         Quiescent           Themal Properties         (C/W)         (C)         (C)         Supply Power (W)         0.756         0.000         0.755           2.3         82.8         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         52.2         5 | - |

Figure 4.Power Consumption of Existing System

## 5.2. Performance Measurement of Proposed System

## 5.2.1. Area Consumption

The area requirements of slice registers, LUT, LUT –flip-flop pairs, bonded IOB buffers are 39,44,39,7,1 respectively as shown in figure 5. Thus the area consumption is reduced from the existing system.

| ISE Project Navigator (M.53d) - D:\WORK_G\ME_2016\AU_T_MDU\VER_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              | system that the                                   | of the                                |                                                 |                  |                 | - 0 - X                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------|---------------------------------------|-------------------------------------------------|------------------|-----------------|----------------------------|--|

| ∑ File Edit View Project Source Process Jools Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              | ▶ ∑ <b>4</b>                                      |                                       |                                                 |                  |                 | - 8                        |  |

| Design ↔ 🗆 🗗 🗙 🌈                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Design Overview     Summary                  |                                                   | Proposed                              | _Main Project Status (                          | 04/11/2017 - :   | 13:18:29)       |                            |  |

| View:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              | Project File:                                     | VER_27.xise                           |                                                 | Errors:          |                 | No Errors                  |  |

| 🙀 🔤 VER_27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🛅 Timing Constraints                         | Module Name:<br>Target Device:                    | Modified<br>xc6vlx75t-3ff484          |                                                 | nentation Stat   |                 | Synthesized<br>No Errors   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pinout Report                                | Product Version:                                  | ISE 12.1                              |                                                 | Warnings:        |                 | 5 Warnings (3 new)         |  |

| E Notified - Modified (Modified.vhd)     E existing work tb - TB ARCHITECTURE (Existing work)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Errors and Warnings                          | Design Goal:                                      | Balanced                              |                                                 | Routing Results: |                 |                            |  |

| proposed_main_tb - TB_ARCHITECTURE (Proposed_N     UUT - Proposed_Main - Proposed_Main (LP_AUT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Parser Messages                              | Design Strategy:<br>Environment:                  | Xilinx Default (un<br>System Settings | • Timing Constraints:     • Final Timing Score: |                  |                 |                            |  |

| PR1 - L1_L2_cache - logic (L1_L2_cache.vhd)     PR2 - Reconfig_memory - Behavioral (ORLB_r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - 👩 Translation Messages<br>- 👩 Map Messages |                                                   |                                       |                                                 |                  |                 |                            |  |